본 논문에서는 UHD 이미지를 실시간으로 처리하는 고성능 방사 왜곡 보정 회로의 구조를 제안한다. 기존 연구에서는 왜곡 보정에 필요한 이미지 데이터에 접근할 때, 이미지 전체를 메모리에...

http://chineseinput.net/에서 pinyin(병음)방식으로 중국어를 변환할 수 있습니다.

변환된 중국어를 복사하여 사용하시면 됩니다.

- 中文 을 입력하시려면 zhongwen을 입력하시고 space를누르시면됩니다.

- 北京 을 입력하시려면 beijing을 입력하시고 space를 누르시면 됩니다.

UHD 이미지를 실시간으로 처리하는 고성능 방사 왜곡 보정 회로 설계 = Design of High-performance Radial Distortion Correction Circuit for Real-time Processing of UHD Images

한글로보기https://www.riss.kr/link?id=A108885939

- 저자

- 발행기관

- 학술지명

- 권호사항

-

발행연도

2023

-

작성언어

Korean

- 주제어

-

등재정보

KCI우수등재

-

자료형태

학술저널

- 발행기관 URL

-

수록면

3-13(11쪽)

- 제공처

-

0

상세조회 -

0

다운로드

부가정보

국문 초록 (Abstract)

본 논문에서는 UHD 이미지를 실시간으로 처리하는 고성능 방사 왜곡 보정 회로의 구조를 제안한다. 기존 연구에서는 왜곡 보정에 필요한 이미지 데이터에 접근할 때, 이미지 전체를 메모리에 저장하고 매 클락마다 메모리에 직접 접근하는 방식을 사용하고 있다. 그러나 이러한 방법은 고해상도 이미지를 처리할 경우 내부 메모리에 이미지 전체를 저장하는 것은 불가능하며, 외부 메모리에 이미지 전체를 저장한다고 하더라도 실제 애플리케이션 상에서 실시간 처리를 위해 매 클락마다 외부 메모리에 접근하는 것은 비현실적이다. 이를 해결하기 위해 본 논문에서 제안하는 회로 구조에서는 캐시 개념을 도입하였다. 접근해야 하는 이미지 픽셀 값을 캐시 메모리에 미리 저장해 둠으로써 외부 메모리 접근 횟수를 크게 감소시켜서 UHD 이미지와 같은 고해상도 이미지를 실시간으로 처리한다. 캐시 메모리는 362K 비트 SRAM으로 구현하였다. 65nm 표준 셀 라이브러리를 사용하여 합성한 결과, 게이트 수는 29,667개이다. 최대 동작주파수는 1,200MHz이고, 4K UHD 이미지를 0.3 GPPS의 속도로 처리함으로써 실시간 처리에 필요한 성능을 만족한다.

다국어 초록 (Multilingual Abstract)

This paper proposes an architecture of a high-performance radial distortion correction circuit that processes UHD images in real time. In previous research, a method of directly accessing the entire image in memory at every clock cycle is commonly emp...

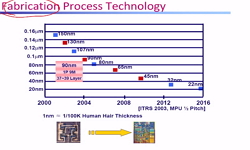

This paper proposes an architecture of a high-performance radial distortion correction circuit that processes UHD images in real time. In previous research, a method of directly accessing the entire image in memory at every clock cycle is commonly employed when accessing the image data necessary for distortion correction. However, this approach becomes impractical when dealing with high-resolution images due to the limitations of internal memory capacity. Even if storing the entire image in external memory, accessing external memory at every clock cycle for real-time processing in the actual application context remains nearly infeasible. To address this issue, the circuit architecture proposed in this paper introduces the concept of caching. The architecture pre-stores the image pixel values that need to be accessed in cache memory, significantly reducing the frequency of external memory accesses. As a result, it becomes possible to handle real-time high-resolution image processing, such as UHD images. The cache memory is implemented using 362K-bit SRAM. The results synthesized using a 65nm standard cell library show that the circuit comprises 29,667 gates, achieves a maximum operating frequency of 1,200MHz, and processes 4K UHD images at a speed of 0.3 GPPS, meeting the performance requirements for real-time processing.

동일학술지(권/호) 다른 논문

-

- 대한전자공학회

- 권 윤 중

- 2023

- KCI우수등재

-

열손실 특성을 갖는 히팅 자켓의 모델 식별과 온도 실험을 통한 검증

- 대한전자공학회

- 남진문

- 2023

- KCI우수등재

-

- 대한전자공학회

- 권세이

- 2023

- KCI우수등재

-

공통모드 아티팩트에 내성을 가진 저전력 저잡음 뇌신호 기록 초퍼 증폭기

- 대한전자공학회

- 유효준

- 2023

- KCI우수등재

DBpia

DBpia