현재 휴대용 장비들이 각광받고 있는 가운데 휴대용 디스플레이 장비들의 수요가 커져가고 있다. 이러한 휴대용 디스플레이 장치들에는 저전력, 고속, 고해상도, 저 면적의 데이터 변환기가...

http://chineseinput.net/에서 pinyin(병음)방식으로 중국어를 변환할 수 있습니다.

변환된 중국어를 복사하여 사용하시면 됩니다.

- 中文 을 입력하시려면 zhongwen을 입력하시고 space를누르시면됩니다.

- 北京 을 입력하시려면 beijing을 입력하시고 space를 누르시면 됩니다.

부가정보

국문 초록 (Abstract)

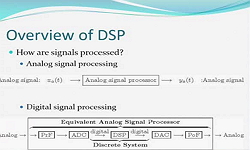

현재 휴대용 장비들이 각광받고 있는 가운데 휴대용 디스플레이 장비들의 수요가 커져가고 있다. 이러한 휴대용 디스플레이 장치들에는 저전력, 고속, 고해상도, 저 면적의 데이터 변환기가 요구된다. 본 논문에서는 이러한 휴대용 장비에 적용이 가능한 저전력 8bit 10MS/s ADC를 구현하였다. 기존의 파이프라인 ADC를 구성하는 MDAC은 연산증폭기를 사용하는데, ADC 전체의 성능을 높이기 위해서는 이 연산증폭기의 설계가 매우 중요하다. 고속 동작을 하려면 연산증폭기의 소모전류를 크게 해야 하고, 고 해상도 동작을 보장하려면 증폭기의 이득을 크게 설계해야 하는 어려움이 있었다. 본 논문에서는 이러한 점을 개선할 수 있는 방법을 제안하였다. 본 논문에서 제안한 회로는 비교기와 전류원을 이용하여 샘플링 데이터 시스템(Sampled data system)에 응용되는 연산증폭기와 같은 동작을 하도록 설계하였다. 제안된 회로의 장점은 기존의 회로에 비해 설계가 용이하고, 전력소모가 적어진다는 것 이다. 또한 본 논문의 회로는 비교기에 존재하는 일정한 지연시간을 통해서 각 단간에 전달되는 전압의 에러를 최소화하고 정밀한 잉여전압(residue)을 전달하도록 하였다. 그리고 각 단의 내부 ADC와 최종단 플래쉬 ADC를 구성하는 동적 비교기의 선 증폭단(Pre-amp stage)에 Differential charge transfer amplifier(DCTA)를 적용하였기 때문에 회로내의 소모전력을 크게 줄일 수 있었다. 제안된 회로는 비교기와 전류원만을 이용하였기 때문에 약 1.8mW이내의 전력을 소모한다. 제안된 8 비트 10MS/s 파이프라인 ADC는 0.18 ㎛ 1P4M 표준 CMOS공정을 사용하여 구현하였다. 칩의 크기는 2.5mm × 1mm이며 전력 소모는 1.8V 전원전압에서 약 1.8 ㎽이다.

다국어 초록 (Multilingual Abstract)

This paper describes a design of 8 bit 10 MS/s low power pipeline analog to digital converter(ADC) which can apply to portable display device. Conventional pipeline ADC uses an opamp in MDAC. To make high performance ADC, the design of high performanc...

This paper describes a design of 8 bit 10 MS/s low power pipeline analog to digital converter(ADC) which can apply to portable display device. Conventional pipeline ADC uses an opamp in MDAC. To make high performance ADC, the design of high performance opamp is required. For high speed operation, the opamp has a high unity gain frequency. And If the ADC can perform high resolution, we make a high gain opamp. Cause by these problems, the design of ADCs are very difficult. Proposed pipeline ADC, which consist of comparator and current source, is able to solve this problems. Because the proposed circuit uses comparator and current source instead of a opamp, it can perform low power operation. In addition, the circuit can reduce power consumption using dynamic comparator in sub-ADC and flash ADC(last stage). The dynamic comparator uses differential charge transfer amplifier(DCTA) for pre-amp. Because the DCTA uses charge transfer technique, the dynamic comparator consumes less power than conventional circuits.

Proposed 8-bit 10MS/s pipeline ADC is implemented with a standard 0.18 ㎛ 1P4M CMOS technology. The size of the circuit is 1mm ⅹ 1.2mm and its power consumption is 1.8mW at 1.8V supply voltage.

목차 (Table of Contents)

- Ⅰ. 서론 1

- 1. 연구 배경 1

- Ⅱ. 기존의 파이프라인 ADC 5

- Ⅲ. 제안된 저전력 파이프라인 ADC 9

- Ⅳ. 제안한 8비트 10MS/s 1.8mW 파이프라인 ADC 설계 14

- Ⅰ. 서론 1

- 1. 연구 배경 1

- Ⅱ. 기존의 파이프라인 ADC 5

- Ⅲ. 제안된 저전력 파이프라인 ADC 9

- Ⅳ. 제안한 8비트 10MS/s 1.8mW 파이프라인 ADC 설계 14

- 1. 전체 블록도 15

- 2. 비교기를 이용한 MDAC 16

- 3. MADC을 구성하는 전류원(Current source) 19

- 4. 비교기 설계 21

- 5. 내부 ADC(Sub-ADC) 설계 23

- 6. 최종단 플래쉬(Flash) ADC의 설계 26

- 7. Differential charge transfer amplifier(DCTA)를 이용한 동적비교기 28

- 8. 바이어스 회로 32

- 9. 디지털 출력의 동기를 위한 래치와 에러 보정회로 설계 34

- Ⅴ. 모의실험 결과 및 Layout 37

- 1. 전체 ADC의 모의실험 결과 37

- 2. 레이아웃(Layout) 40

- 3. 성능 비교 41

- Ⅵ. 결론 42

- 참고문헌 44

- Abstract 47