정보화 사회가 진행되어감에 따라 카메라 센서, 디지털 카메라, 휴대폰, 영상 관련디지털 기기들이 증가하고 이로 인하여 영상정보 서비스 기술의 중요성이 크게 부각되었다. 특히 멀티미디...

http://chineseinput.net/에서 pinyin(병음)방식으로 중국어를 변환할 수 있습니다.

변환된 중국어를 복사하여 사용하시면 됩니다.

- 中文 을 입력하시려면 zhongwen을 입력하시고 space를누르시면됩니다.

- 北京 을 입력하시려면 beijing을 입력하시고 space를 누르시면 됩니다.

면적효율적인 JPEG 베이스라인 프로파일 코어의 HDL 설계 = HDL Design of an Area Efficient JPEG Baseline Profile Core

한글로보기https://www.riss.kr/link?id=T11591982

- 저자

-

발행사항

오산 : 한신대학교 대학원, 2009

- 학위논문사항

-

발행연도

2009

-

작성언어

한국어

- 주제어

-

발행국(도시)

경기도

-

형태사항

vii, 55 p. ; 26cm

- 소장기관

-

0

상세조회 -

0

다운로드

부가정보

국문 초록 (Abstract)

정보화 사회가 진행되어감에 따라 카메라 센서, 디지털 카메라, 휴대폰, 영상 관련디지털 기기들이 증가하고 이로 인하여 영상정보 서비스 기술의 중요성이 크게 부각되었다. 특히 멀티미디어 응용서비스 기술에서는 영상 정보가 필수적인데, 그 영상 정보의 양이 너무 방대하여 압축 부호화를 하여 사용되고 있다.

본 논문에서는 정지영상압축 방법 중 JPEG표준에서 제시한 4가지 동작 모드 중 베이스라인을 기반으로 하는 JPEG 알고리즘을 연구하여 Motion JPEG에서 동작 가능한 IP를 C언어를 통해 시뮬레이션하고 최적화된 결과를 VHDL로 구현하였다.

인코더 설계 시 8*8 DCT 계수 데이터와 8*1 영상 데이터 값을 곱셈 연산 하는 방법이 아닌, 4*4 DCT 계수 데이터와 4*1 영상 데이터의 행렬 곱셈 연산을 통해 DCT를 병렬처리 하여 고속화 및 효율성을 증가 시켰다. 1D-DCT의 결과를 전치하기 위한 행렬전치 모듈내의 결과 값 저장 공간은 RAM을 사용하지 않고 Register Array를 이용하여 면적 효율적으로 설계하였으며, 2D-DCT의 결과를 바로 지그재그 순서로 재배치함에 따라 전체적인 지연시간을 단축시킬 수 있었다. 또한 허프만 테이블의 규칙성을 이용 상위비트의 연속적인 ‘1’값을 고정적으로 마킹하여 ROM 테이블의 용량을 효율적으로 사용함으로써 면적을 최소화 시켰다.

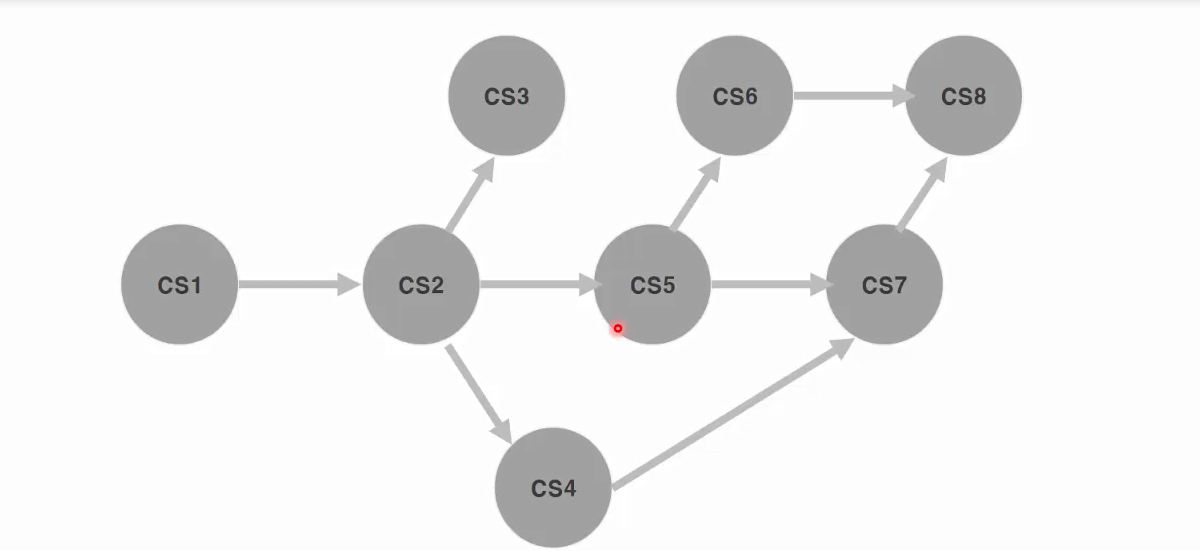

디코더 설계 시 Motion JPEG의 응용분야가 주로 보안 및 교통관련 환경에서 무선통신 방식을 사용하는 경우가 빈번하게 이루어짐을 감안 불규칙적 스트리밍 방식 입력 조건하에 동작해야 함을 주안점으로 설계하였다. 이를 위해 전체 모듈을 조율하는 FSM에서 파이프라인 방식의 제어를 통해 전체적인 모듈 동작의 효율성을 증가시켰고 불필요한 지연을 최소화 하였다. 또한 내부에 프레임 메모리를 사용하지 않고 블록사이즈 수준의 버퍼 내에서 입력과 처리가 이루어지는 구조로 설계함으로써 면적효율성을 증가시켰다.

JPEG IP는 Xilinx ISE 7.1i 툴을 이용하여, VHDL 언어로 설계하였고 설계한 모듈은 ModelSim-SE 6.1을 이용하여 검증을 하였다. Xilinx XC3S2000-4fg676 FPGA 환경에서 JPEG 인코더는 65.867㎒의 동작속도에 98,853개의 게이트가 사용되었고 최초 약170 클록 이후에는 연속적으로 데이터가 출력되게 된다. JPEG 디코더는 66.130㎒의 동작속도에 77,121개의 게이트가 사용되었고 가변길이 데이터 및 불규칙한 입력에 따라 가변적인 출력타이밍을 갖도록 설계되었다.

최종적으로 인터페이스 검증을 위해 TLA5201 Logic Analyzer를 통한 I2C 및 SPI bus구조 연구를 통한 카메라와 FPGA간의 통신 및 DSPic와 JPEG간의 인터페이스 방식에 대해 분석하였다. 또한 CMOS 카메라로부터 입력 받은 YCbCr 4:4:4 방식의 QVGA(320×240)급 영상 데이터를 JPEG의 입력 방식에 맞게 8*8블록단위 입력방식에 맞춰 4:2:2 또는 4:2:0로 재배열하는 Line Buffer를 설계하였다. 이후 FPGA를 통한 JPEG 인코딩 및 디코딩을 거쳐 QVGA(320×240) 18bit RGB LCD에 초당 15프레임의 동영상을 출력하는 인터페이스 검증을 완료하였다.

본 연구에 사용된 Motion JPEG은 보안장비나 교통관련 영상 또는 장난감등의 카메라와 관련된 동영상 캡처에 응용하기에 적합하다.

다국어 초록 (Multilingual Abstract)

As an information-oriented society is progressing, the importance of video information service has been embossed due to increase of camera sensor, digital camera, cell phone and digital equipments related with video. Especially for application service...

As an information-oriented society is progressing, the importance of video information service has been embossed due to increase of camera sensor, digital camera, cell phone and digital equipments related with video. Especially for application service technology of multimedia, video information is necessary but it is tremendous in quantity of video information. Hence compression encoding is used for video applications.

In this thesis, JPEG algorithm based on baseline mode is studied among 4 operation modes proposed in JPEG standard. IP applicable to Motion JPEG is to be simulated by C language and optimum result is implemented by VHDL.

In the encoder design, DCT(Discrete Cosine Transform) is processed in parallel. High-speed and efficiency are enhanced through not multiplying 8*8 DCT coefficients by value of 8*1 video data but multiplying matrix data of 4*4 DCT coefficients by 4*1 video data.

The block storing and transposing the result of 1D-DCT is efficiently designed using register array, not using RAM.

As result of 2D-DCT is immediately arranged in zigzag, delay time could be reduced. Also the area is minimized by use of ROM table capacity efficiently through marking continuous value of ‘1’ on MSB part using regulation by Huffman table.

As application field of Motion JPEG frequently uses the wireless communication in environment related with security and transport when designing decoder, it is designed focusing on operation under the input condition of irregular streaming.

Through the control of pipeline method in FSM, efficiency of entire module operation is increased and unnecessary delay is minimized. Also area efficiency is increased by designing the module possible to input and manipulate in buffer of block size level not by using internal frame memory.

JPEG IP is designed in VHDL language using Xilinx ISE 7.1i and the designed module is verified by ModelSim-SE 6.1.

In environment of Xilinx XC3S2000-4fg676 FPGA, JPEG encoder is implemented in 98,853 gates at 65.867㎒ of operation speed and data is continuously outputted after about 170 clocks. JPEG decoder is implemented in 77,121 gates at 66.130㎒ of operation speed. To cope with irregular and variable length input stream, it is designed to get a variable output timing.

Finally, I²C and SPI bus protocols by TLA5201 Logic Analyzer are studied on interface applications among camera, FPGA and DSPic.

Also the line buffer is designed rearranging YCbCr 4:4:4 format from CMOS camera for QVGA(320×240) resolution into YCbCr 4:2:2 or 4:2:0 format of 8*8 block unit suitable for JPEG input processing order.

After that, verification of interface is completed displaying video of 15 frames per second on QVGA(320×240) 18-bit RGB LCD by JPEG encoding and decoding by FPGA.

Motion JPEG implemented in this thesis is suitable for applications of video capture related with video, camera of toy, security equipment, transport and so on.

목차 (Table of Contents)

- Ⅰ. 서론 = 1

- Ⅱ. JPEG 알고리즘 = 2

- 2.1. 코덱별 기술 비교 연구 = 2

- 2.2. JPEG 전체 흐름 = 6

- 2.3. 변환 /양자화 = 7

- Ⅰ. 서론 = 1

- Ⅱ. JPEG 알고리즘 = 2

- 2.1. 코덱별 기술 비교 연구 = 2

- 2.2. JPEG 전체 흐름 = 6

- 2.3. 변환 /양자화 = 7

- 2.4. 엔트로피 코딩 = 11

- Ⅲ. 베이스라인 기반의 JPEG 설계 = 15

- 3.1. JPEG 인코더 = 15

- 3.1.1. 인코더 전체 모듈 = 15

- 3.1.2. DCT 모듈 설계 = 16

- 3.1.3. 엔트로피 인코딩 모듈 설계 = 18

- 3.2. JPEG 디코더 = 23

- 3.2.1. 디코더 전체 모듈 = 23

- 3.2.2. 엔트로피 디코딩 모듈 설계 = 24

- 3.2.2.1. 불규칙한 데이터 입력 = 24

- 3.2.2.2. 가변적인 데이터 길이 처리 = 24

- 3.2.2.3. AC 계수값 디코딩 = 25

- 3.2.2.4. 엔트로피 디코더 전체 블록도 = 27

- 3.2.3. InverseDCT 모듈 설계 = 29

- 3.3. JPEG 헤더 = 30

- 3.3.1. MotionJPEG 데이터 전송 포멧 = 30

- 3.3.2. JPEG 헤더 분석 = 31

- 3.3.3. 헤더 파싱 = 33

- Ⅳ. 인터페이스 = 38

- 4.1. 전체 인터페이스 = 39

- 4.2. 보드 레벨의 검증 = 39

- 4.3. I²C bus통신 = 40

- Ⅴ. 성능평가 = 41

- 5.1. 인코더 설계 결과 = 42

- 5.2. 디코더 설계 결과 = 46

- Ⅵ. 결론 = 50

- 참고문헌 = 52

- ABSTRACT = 54